笔者使用GMAC的主要场景为SOC

内部内置了GMAC,并通过MDIO+RGMII接口和外部PHY芯片通信,通过MDIO配置PHY的寄存器,通过RGMII和PHY收发数据。故对MII、RMII、GMII不熟悉,不进行过多描述。该文主要是结合网上已有的博文资料和笔者自身的调试经验进行的总结归纳。

该文主要分为三部分,第一部分是介绍MDIO接口及其数据格式和时序规范。该部分内容涵盖大部分日常调试中需要了解的知识,在调试过程中可查阅该部分分析MDIO硬件时序上是否不妥之处。第二部分是介绍RGMII接口及时序规范。第三部分为个人经验总结。

文档链接:

https://download.csdn.net/download/ty1121466568/85932043

MDIO(Management Data Input/Output)-管理数据输入输出接口,

也叫串行管理接口-SMI(Serial Management

Interface)、介质无关接口管理接口-MIIM(Media Independent Interface Management

interface), 定义在IEEE802.3以太网标准规范第22章节, 实现网口MAC(Media Access

Control)对网口PHY(Ehternet Physical Layer)芯片的管理与控制,

比如网口速率设置、网口双工模式设置、自协商使能控制等等。简而言之,MDIO用于MAC对PHY寄存器的读写操作。

图1为MDIO应用框图。STA设备通过MDIO接口与PHY通信。

STA:

STA(StationManagement)为主控设备,比如MCU、MAC、ONU等。PHY为从设备。一个STA最多管理32个PHY。

MDC:

MDIO时钟线。MDC要求由MAC输出,是非周期性的,即不要求提供固定频率的时钟,对于PHY芯片则作为输入,以在上升沿触发MDIO的读写。IEEE标准802.3规定MDC最小的时钟周期为400ns,即最高频率为2.5MHz,实际上,MDC的频率可以超过规定的最高频率2.5MHz,比如Marvell的88E1512最大支持12MHz的MDC。MDC的时钟频率可以是DC-2.5MHz,一般建议1.0MHz-2.5MHz。

MDIO:

MDIO数据线。通常MDIO会通过电阻上拉至接口电源。MDIO是双向的,只支持一个MAC连接最多32个PHY的连接方式,且MAC作为master,PHY作为slave。在写PHY寄存器的时候,由MAC驱动MDIO向PHY写入数据;在读PHY寄存器时,前半段由MAC驱动发送寄存器地址,后半段由PHY驱动回复寄存器的值。

注意,在一个STA对应多个PHY时,不同PHY通过PHY的地址来区分。

MDIO有两种模式:俗称1G MDIO和XG MDIO。1G MDIO由IEEE 802.3

Clause22定义,主要应用于千兆/百兆的以太PHY,XG MDIO由IEEE 802.3

Clause45定义,主要用于千兆以上的以太PHY。下面以Clause22为例。

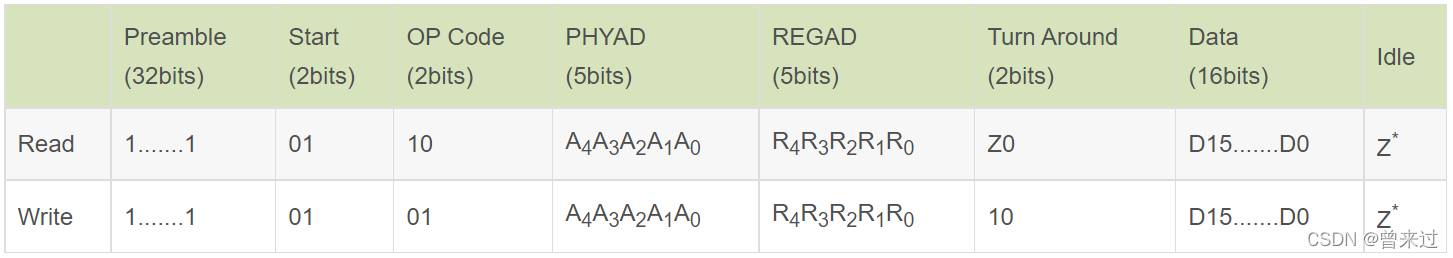

MDIO数据格式定义在IEEE 802.3以太网标准中,如下图所示(数据传输顺序为从左至右):

图2 MDIO数据格式

上图中*表示高阻态,这时MDIO的状态由一个外部的1.5KΩ电阻决定。

Preamble+Start:32bits的前导码以及2bit的开始位。

OP Code:2bits的操作码,10表示读,01表示写。

PHYAD:5bits的PHY地址,一般PHY地址从0开始顺序编号,例如6口switch中PHY地址为0-5。

REGAD:5bits的寄存器地址,即要读或写的寄存器。

Turn

Around:2bits的TA,在读命令中,MDIO在此时由MAC驱动改为PHY驱动,并等待一个时钟周期准备发送数据。在写命令中,不需要MDIO方向发生变化,则只是等待两个时钟周期准备写入数据。

Data:16bits数据,在读命令中,PHY芯片将读到的对应PHYAD的REGAD寄存器的数据写到Data中,在写命令中,MAC将要写入对应PHYAD的REGAD寄存器的值写入Data中。

Idle:空闲状态,此时MDIO无源驱动,处高阻状态,但一般用上拉电阻使其处在高电平。

典型的MDC/MDIO读操作:

图3 MDC/MDIO读操作

典型的MDC/MDIO写操作:

图4 MDC/MDIO写操作

如果是STA(MAC层设备)驱动MDIO,则MDIO相对于MDC上升沿,至少要有10ns的建立时间(Setup

Time)和10ns的保持时间(Hold Time)。如下图所示:

图5 MAC驱动MDIO

如果MDIO是由MMD(PHY层设备)驱动的,则MDIO相对于MDC的Tco(Clock to Output

Delay)的范围是0ns~300ns。如下图所示:

图6 PHY驱动MDIO

RGMII(Reduced Gigabit Media Independant

Interface),精简GMII接口。相对于GMII相比,RGMII具有如下特征:

发送/接收数据线由8条改为4条

TX_ER和TX_EN复用,通过TX_CTL传送

RX_ER与RX_DV复用,通过RX_CTL传送

1 Gbit/s速率下,时钟频率为125MHz

100 Mbit/s速率下,时钟频率为25MHz

10 Mbit/s速率下,时钟频率为2.5MHz

信号定义如下:

图7 RGMII 信号表

图8 RGMII 信号连接图

1000M模式下,TXC/RXC时钟为125Mhz,为了达到1000Mbit的传输速率,TXD/RXD信号线在时钟上升沿发送接收TXD[3:0]/RXD[3:0],在时钟下降沿发送接收TXD[7:4]/RXD[7:4]。10M/100M模式下,在时钟上升沿发送和接收数据。

图9 RGMII AC Characteristics

图10 RGMII Multiplexing and Timing

从上边的时序图分析,数据在时钟的边沿变化。因此如果不做额外处理,接收端无法稳定采样。为了解决这一问题,常见的做法是为时钟信号添加延时,使其边沿对准数据总线的稳定区间,接收端满足TSKEWR的电气要求。可以在控制器端、PCB走线以及PHY芯片内部添加时钟偏移。一般情况下MAC控制器端或PHY芯片内部添加时钟延时。

时钟延时结构图如下:

图11 时钟延时结构图

MAC控制器端添加时延:一般该情况下都是SOC内部对MAC发送/接收的时钟信号添加偏移,具体是多少视SOC和其配置而定。

PCB走线添加时延:在过去由于MAC端和PHY端技术所限,添加时延会提高成本,故用PCB走线来控制时延,目前基本上已不再采用改方式。

PHY芯片内部添加时延:目前的PHY基本上都是支持该功能,对TXC/RXC在PHY芯片内部添加时延。

笔者使用GMAC的主要场景为SOC 内部内置了GMAC,目前主要用Synopsys的DesignWare Cores

Ethernet MAC Universal和DesignWare Cores Ethernet Quality-of-Service这两款。

使用GMAC前,需要把GMAC模块的相关时钟使能。

通过GPIO 对PHY进行复位,检查PHY 是否有RX_CLK输出到MAC。笔者使用的这两个GMAC

IP软件复位需要PHY的RX_CLK输入,否则将1.配置GMAC寄存器进行软件将失败,无法复位;2.若GMAC和PHY已配置双工模式和传输速率,若RX_CLK频率不对,将导致GMAC无法产生收发包中断和无法收发包。

配置GMAC寄存器。配置GMAC其他寄存器前最好配置软件复位的寄存器,让GMAC复位,再配置其他。此处应注意,一般GMAC都有报文过滤的功能,笔者使用的GMAC默认情况下收到的报文目标MAC地址和配置的该GMAC

MAC地址一致,或者配置GMAC的报文过滤为通过所有报文,报文才能通过。软件复位依赖上述的RX_CLK。

GMAC收发缓冲区、收发描述符地址要和DMA cache line对齐,GMAC

收发包依赖DMA,若不对齐,则有可能无法收发包或收发包异常(包括但不限于无法触发收发包中断,收发描述符OWN位状态无变化,收发包数据错误等现象偶现/必现)。

GMAC收发包前,需根据情况做invalidate cache, flush

cache的操作,若省略这一步,可能有cache一致性问题,导致无法收发包或收发包异常(包括但不限于无法触发收发包中断,收发描述符OWN位状态无变化,收发包数据错误等现象偶现/必现)。

GMAC确保正确工作之后,可手动简单构建一个无意义的包,比如数据为多个0xFF,0X55,0XAA序列的包。然后设置GMAC速率为10M,用逻辑分析仪抓取波形,对比RGMII时序图检查GMAC简单发包时序是否正确。

MDIO主要用来读写PHY寄存器,达到管理,配置PHY的作用。一般情况下若MDIO读写异常,则建议检查其硬件时序是否正确。

笔者所用的两个GMAC

IP文档中建议将MDC时钟通过分频配置为1.0MHz-2.5MHz。其MDC时钟通过对CSR时钟分频得到(仅限于上述IP)。

使用MDIO读取PHY的ID寄存器,对比结果和PHY的数据手册是否一致。

使用MDIO读-写-读PHY的控制寄存器,看PHY的寄存器的值是否改变。

若上述读写操作失败,可使用逻辑分析仪获取MDIO接口的波形,对比MDIO接口时序排查哪一步出现问题。具体对比过程和问题不再详细描述。

在确保GMAC本身编码正确,MDIO读写正确的情况下,可对PHY时序的收发时钟延时进行调整。速率越高,MAC和PHY对时钟、时序要求越高,此处建议从简单入手,从10M、100M、1000M的TX/RX依次向上调试。此处需注意MAC和PHY的双工模式(全双工和半双工),速率应保持一致,否则将会收发包错误。此外,调整TXC/RXC时钟延时的最终目的都是为了让接受端时钟边沿对准数据总线的稳定区间,能够准确采样读取数据。即满足TSKEWR的电气要求。实际应用中,有可能SOC内部布线、PCB布线、PHY芯片的内部具体电路和理想情况下有差异,导致不需要配置额外的时钟延时就能正确收发报文的情况存在。故调试过程中主要思想是以接收端满足TSKEWR的电气要求为准,具体时钟延时调试根据具体情况灵活配置。需注意,大多数PHY默认配置都是加了延时的,若自己调试延时最好自己手动关闭再调试。

调试GMAC的TX,可手动构建一个ARP报文。发送该ARP报文,在Wireshark上抓包看是否能捕获到。Wireshark上可设置过滤器为”arp

and

eth.addr==66:34:b0:23:ce:ad”来只看ARP报文,减少干扰项,其中eth.addr后跟自己组的ARP报文的源MAC地址。或直接用其他设备连接该PHY,看是否收到报文。

若其他设备或PC主机收不到GMAC发出的ARP报文,可进行如下顺序调试,直到发包正常:

关闭SOC侧TXC时钟延时,关闭PHY侧的TXC时钟延时;

关闭SOC侧TXC时钟延时,打开PHY侧的TXC时钟延时,若PHY侧时钟延时可配置,则从小到大依次配置;

打开SOC侧TXC时钟延时,关闭PHY侧的TXC时钟延时,若SOC侧时钟延时可配置,则从小到大依次配置;若SOC和PHY的时钟延时可配置范围接近,该步骤效果和步骤b一致,该步骤可省略;

打开SOC侧TXC时钟延时,打开PHY侧的TXC时钟延时,若SOC侧和PHY侧时钟延时均可配置,则将PHY侧延时配置到最大,将SOC侧延时从小到大依次配置。直到两个时钟都到最大延时。

若SOC,PHY加正向延时无效果,则可以考虑是否是整个链路中延时太大,需要加负的延时,若PHY或SOC支持该操作,则可配置为TXC负延时进行调试。部分PHY支持该功能。

若上述步骤均失败,可尝试使用示波器抓取PHY侧的TX相关信号,看波形的延时是否ok。

调试GMAC的RX,在PC上组建一个ARP应答包(笔者使用ostinato-0.8来进行组包发包),或直接用其他设备连接该PHY,一直发送固定报文,看GMAC是否收到该报文。具体时钟调试策略和调试TX一致。

调试过程中强制指定PHY的速率和双工模式

为了减少干扰,笔者调试过程中一般都是强制指定PHY工作的速率和双工模式,一般可通过配置PHY的advertise寄存器,将其他模式全部失能,连接其他设备自协商时就只会自协商成指定模式。笔者试过强制指定速率和双工模式,然后关闭自协商,但是部分phy一旦关闭自协商,速率总是为默认值,无法修改,笔者学艺不精,选择自协商成指定模式。

PHY的时钟延时配置

不同PHY时钟延时配置不尽相同,有的时钟延时只能开和关,延时时间是固定的2ns,有的可灵活配置为N*150ps,有的能配置为负延时(-1*150ps),有的既有固定时间配置项又有灵活时间配置项,故具体调试过程中需自己阅读PHY的寄存器。

,将其他模式全部失能,连接其他设备自协商时就只会自协商成指定模式。笔者试过强制指定速率和双工模式,然后关闭自协商,但是部分phy一旦关闭自协商,速率总是为默认值,无法修改,笔者学艺不精,选择自协商成指定模式。

PHY的时钟延时配置

不同PHY时钟延时配置不尽相同,有的时钟延时只能开和关,延时时间是固定的2ns,有的可灵活配置为N*150ps,有的能配置为负延时(-1*150ps),有的既有固定时间配置项又有灵活时间配置项,故具体调试过程中需自己阅读PHY的寄存器。

版权说明:如非注明,本站文章均为 扬州驻场服务-网络设备调试-监控维修-南京泽同信息科技有限公司 原创,转载请注明出处和附带本文链接。

请在这里放置你的在线分享代码